## Projeto 1 - Introdução à Lógica Digital

SSC-117- 1° Semestre de 2015

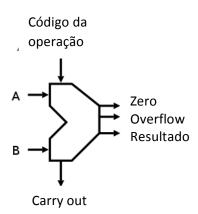

O projeto consiste na implementação de uma Unidade Lógica e Aritmética (ULA) em hardware utilizando como base o dispositivo FPGA (Field-Programmable Gate Array). A ULA deverá operar sobre dados com largura de 8 bits e representação numérica em complemento de dois. As operações lógicas e aritméticas a serem implementadas são as seguintes, com os seus respectivos códigos de operação representados entre os parênteses:

Lógicas: NOT (0001), AND (0010), OR (0011), NAND (0100), NOR (0101), XOR (0111)

Aritméticas: ADD (1000), SUB (1001)

A ULA deverá ser vista como um único componente de hardware, tendo com entrada os valores para os operandos A e B e os códigos de operação e como saída o resultado e a indicação de overflow.

Os valores de A e B e os códigos de operação deverão estar previamente armazenados em uma única memória ROM inicializada via arquivo .mif ou .hex. Os sinais de controle da memória serão gerados manualmente pelas chaves existentes na placa de FPGA, conforme detalhes vistos nas aulas de laboratório.

O resultado deverá ser exibido em displays de 7 segmentos existentes na placa de FPGA em valores hexadecimal e os bits de status em LEDs individuais da mesma placa.

## **A**VALIAÇÃO

A nota final do projeto será dada por:

$$N_{final} = N_{arguição} * (0.7 * N_{projeto} + 0.3 * N_{relatório})$$

A entrega do projeto deve ser feita até 14/05/2015. A arguição será individual e será feita no momento da entrega, mas todos os membros do grupo deverão estar presentes.

O relatório deve conter as seguintes seções:

- Capa

- Introdução

- Descrição da ULA

- Simulação das operações no Modelsim

- Conclusões

O relatório deve ser entregue no formato .pdf juntamente com os arquivos fonte do projeto que serão copiados no dia da entrega.