### ICMC - USP

Introduction to VHDL (part 2 of 2)

Prof. Vanderlei Bonato - <a href="mailto:vbonato@icmc.usp.br">vbonato@icmc.usp.br</a>

# Summary

- Data Types

- Assignments

- Data Conversions

- Operators

- Component Instantiation

- Bi-directional Pins

- Exercises

# **Data Types**

| Data types                    | Synthesizable values                        |

|-------------------------------|---------------------------------------------|

| BIT, BIT_VECTOR               | '0', '1'                                    |

| STD_LOGIC, STD_LOGIC_VECTOR   | 'X', '0', '1', 'Z' (resolved)               |

| STD_ULOGIC, STD_ULOGIC_VECTOR | 'X', '0', '1', 'Z' (unresolved)             |

| BOOLEAN                       | True, False                                 |

| NATURAL                       | From 0 to $+2$ , 147, 483, 647              |

| INTEGER                       | From $-2,147,483,647$ to $+2,147,483,647$   |

| SIGNED                        | From $-2,147,483,647$ to $+2,147,483,647$   |

| UNSIGNED                      | From 0 to $+2,147,483,647$                  |

| User-defined integer type     | Subset of INTEGER                           |

| User-defined enumerated type  | Collection enumerated by user               |

| SUBTYPE                       | Subset of any type (pre- or user-defined)   |

| ARRAY                         | Single-type collection of any type above    |

| RECORD                        | Multiple-type collection of any types above |

# **Dealing with Data Types**

```

TYPE byte IS ARRAY (7 DOWNTO 0) OF STD LOGIC;

-- 1D

-- array

TYPE mem1 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD LOGIC;

-- 2D

-- array

TYPE mem2 IS ARRAY (0 TO 3) OF byte;

-- 1Dx1D

-- array

TYPE mem3 IS ARRAY (0 TO 3) OF STD LOGIC VECTOR(0 TO 7); -- 1Dx1D

-- array

-- scalar signal

SIGNAL a: STD LOGIC;

-- scalar signal

SIGNAL b: BIT;

-- 1D signal

SIGNAL x: byte;

SIGNAL y: STD LOGIC VECTOR (7 DOWNTO 0);

-- 1D signal

SIGNAL v: BIT VECTOR (3 DOWNTO 0);

-- 1D signal

SIGNAL z: STD LOGIC VECTOR (x'HIGH DOWNTO 0);

-- 1D signal

SIGNAL w1: mem1;

-- 2D signal

-- 1Dx1D signal

SIGNAL w2: mem2;

-- 1Dx1D signal

SIGNAL w3: mem3;

```

# **Scalar Assignments**

8/20/13 5

# **Vector Assignments**

```

x <= "111111110";

y \le ('1','1','1','1','1','1','0','Z');

z <= "11111" & "000";

x \ll (OTHERS => '1');

y \le (7 = > '0', 1 = > '0', OTHERS = > '1');

z \ll y;

y(2 DOWNTO 0) \le z(6 DOWNTO 4);

w2(0)(7 DOWNTO 0) <= "11110000";

w3(2) \le y;

z \le w3(1);

z(5 \text{ DOWNTO } 0) \le w3(1)(2 \text{ TO } 7);

w3(1) \le "00000000";

w3(1) \le (OTHERS => '0');

w2 <= ((OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0'));

(OTHERS=>'0'), (OTHERS=>'0'));

w1 <= ((OTHERS=>'Z'), "11110000", "11110000", (OTHERS=>'0'));

```

## **llegal Assignments**

```

----- Illegal scalar assignments: ------

-- type mismatch (BIT x STD_LOGIC)

b \le a;

w1(0)(2) \le x(2); -- index of w1 must be 2D

w2(2,0) \le a;

-- index of w2 must be 1Dx1D

----- Illegal array assignments: -----

-- type mismatch

x \le y;

-- wrong direction of y

y(5 \text{ TO } 7) \le z(6 \text{ DOWNTO } 0);

w1 \le (OTHERS => '1');

-- w1 is a 2D array

w1(0, 7 DOWNTO 0) \le "1111111111"; -- w1 is a 2D array

w2 \ll (OTHERS => 'Z');

-- w2 is a 1Dx1D array

w2(0, 7 DOWNTO 0) <= "11110000"; -- index should be 1Dx1D

```

### **DOWNTO** and **TO**

```

SIGNAL x: BIT;

-- x is declared as a one-digit signal of type BIT.

SIGNAL y: BIT VECTOR (3 DOWNTO 0);

-- y is a 4-bit vector, with the leftmost bit being the MSB.

SIGNAL w: BIT VECTOR (0 TO 7);

-- w is an 8-bit vector, with the rightmost bit being the MSB.

x \le '1':

-- x is a single-bit signal (as specified above), whose value is

-- '1'. Notice that single quotes (' ') are used for a single bit.

y \le "0111";

-- y is a 4-bit signal (as specified above), whose value is "0111"

-- (MSB='0'). Notice that double quotes (" ") are used for

-- vectors.

w \le "01110001";

-- w is an 8-bit signal, whose value is "01110001" (MSB='1').

```

### **Bit Levels**

• BIT (and BIT\_VECTOR): 2-level logic ('0', '1')

STD\_LOGIC (and STD\_LOGIC\_VECTOR): 8-valued logic system introduced in the IEEE 1164 standard.

```

Ϋ́,

Forcing Unknown

(synthesizable unknown)

(synthesizable logic '1')

·0'

Forcing Low

Forcing High

'1'

(synthesizable logic '0')

'Ζ'

High impedance

(synthesizable tri-state buffer)

'W'

Weak unknown

'L'

Weak low

'H'

Weak high

٠_,

Don't care

```

Most of the std\_logic are intended for simulation only!

### **ULOGIC**

- STD\_ULOGIC (STD\_ULOGIC\_VECTOR): 9-level logic system introduced in the IEEE 1164 standard ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-').

- STD\_LOGIC system described above is a subtype of STD\_ULOGIC. The latter includes an extra logic value, 'U', which stands for unresolved. Thus, contrary to STD\_LOGIC, conflicting logic levels are not automatically resolved here, so output wires should never be connected together directly. However, if two output wires are never supposed to be connected together, this logic system can be used to detect design errors.

### SIGNED and UNSIGNED

- Their syntax similar to STD\_LOGIC\_VECTOR

- SIGNED and UNSIGNED are intended mainly for arithmetic operations

- Logic operations are not allowed

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

### **Data Conversion**

- VHDL does not allow direct operations between data of different types

- Conversions are necessary

- Several data conversion functions can be found in the std\_logic\_arith package of IEEE library

### std\_logic\_arith Conversion Functions

- conv\_integer(p): Converts a parameter p of type INTEGER, UNSIGNED, SIGNED, or STD\_ULOGIC to an INTEGER value. Notice that STD\_LOGIC\_ VECTOR is not included.

- conv\_unsigned(p, b): Converts a parameter p of type INTEGER, UNSIGNED,

SIGNED, or STD\_ULOGIC to an UNSIGNED value with size b bits.

- conv\_signed(p, b): Converts a parameter p of type INTEGER, UNSIGNED,

SIGNED, or STD\_ULOGIC to a SIGNED value with size b bits.

- conv\_std\_logic\_vector(p, b): Converts a parameter p of type INTEGER, UN-SIGNED, SIGNED, or STD\_LOGIC to a STD\_LOGIC\_VECTOR value with size b bits.

# **Operators**

| Operator type | Operators                                     | Data types                                                                        |

|---------------|-----------------------------------------------|-----------------------------------------------------------------------------------|

| Assignment    | <=, :=, =>                                    | Any                                                                               |

| Logical       | NOT, AND, NAND,<br>OR, NOR, XOR, XNOR         | BIT, BIT_VECTOR,<br>STD_LOGIC, STD_LOGIC_VECTOR,<br>STD_ULOGIC, STD_ULOGIC_VECTOR |

| Arithmetic    | $+, -, *, /, **$ (mod, rem, abs) $^{\bullet}$ | INTEGER, SIGNED, UNSIGNED                                                         |

| Comparison    | =, /=, <, >, <=, >=                           | All above                                                                         |

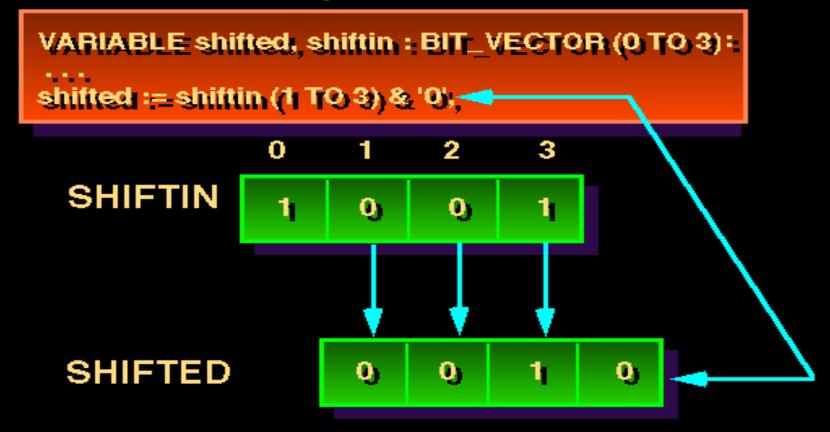

| Shift         | sll, srl, sla, sra, rol, ror                  | BIT_VECTOR                                                                        |

| Concatenation | &, (,,,)                                      | Same as for logical operators, plus SIGNED and UNSIGNED                           |

#### The concatentation operator &

#### The exponentiation operator \*\*

```

x_i := 5^{**}5, --- 5^{5}, QK

y_i := 0.5^{**}3, --- 0.5^{5}, QK

x_i := 4^{**}0.5, --- 4^{5}0.5, bad

y_i := 0.5^{**}(-2), --- 0.5^{5}(-2), QK

```

# Component instantiation (Structural VHDL)

```

component fifo cam is

port(

data

: in STD_LOGIC_VECTOR (31 downto 0);

: in STD LOGIC;

wrreq

: in STD LOGIC;

rdreg

: in STD LOGIC;

rdclk

: in STD LOGIC;

wrclk

: in STD LOGIC;

aclr

: out STD LOGIC VECTOR (31 downto 0);

q

: out STD LOGIC;

rdempty

: out STD LOGIC );

wrfull

end component;

```

fifo: fifo\_cam port map(pixel,'1',read\_cs,clk\_n,ready\_pixel,aclr\_fifo,readdata,waitrequest,fifofull);

# Bidirectional pin

```

ENTITY proc eld2 is

PORT(clk, rst

: in STD LOGIC;

data

: inout STD LOGIC VECTOR(7 downto 0);

: buffer STD LOGIC;

web oeb

address

: out STD_LOGIC_VECTOR(7 downto 0);

: out STD LOGIC VECTOR(7 downto 0);

pc out, ir out

: out STD_LOGIC_VECTOR(2 downto 0)

saida

END proc eld2;

signal ACC : std logic vector(7 downto 0);

web oeb <= '1'; --1 escreve e 0 lê da mem.

data <= ACC WHEN web oeb='1' else "ZZZZZZZZZ";

web oeb <= '0'; --1 escreve e 0 lê da mem.

ACC <= data;

```

## **Tips**

The ENTITY name and the file name must be the same

- Physical and time data types are not synthesizable for FPGAs

- ohm, kohm

- fs, ps, ns, um, ms, min, hr

### And more ...

#### Function

- Produce a single return value

- Requires a RETURN statement

#### Procedure

- Produce many output values

- Do not require a RETURN statement

#### Testbench

- Generate stimulus for simulation

- Compare output responses with expected values

# Implemente em VHDL os seguintes componentes

- FFs do tipo D, T e JK

- Registrador de deslocamento da direita para a esquerda

- Conversor de binário para display de 7 segmentos

- Crie um componente somador completo de 1 bit e instancie esse mesmo componente para formar um somador/subtrator de 8 bits do tipo ripple-carry. Considere que os números estão em complemento de 2; e para o controle da operação utilize C=0 para adição e C=1 para subtração. Indique também overflow. Utilize STD\_LOGIC\_VECTOR para os sinais de entrada e saída

### References

Pedroni, Volnei A. Circuit Design with VHDL, MIT Press, 2004

- DARPA/Tri-Services RASSP Program

- http://www.vhdl.org/rassp/

Brown, S. and Vranesic, Z.. Fundamentals of Digital Logic with VHDL Design, 2<sup>nd</sup> Ed., P. 939, 2005.