### USP - ICMC - SSC

## SSC0510 - Arquitetura de Computadores

Professor responsável: Fernando Santos Osório E-mail: fosorio@icmc.usp.br Semestre: 2010/2 fosorio@gmail.com

Horário: Quarta 21h00 Web: http://www.icmc.usp.br/~fosorio/

# LISTA DE EXERCÍCIOS - Nro. 01

### [Arquiteturas Clássicas]

- 1. Descreva as principais características e compare as Arquiteturas de Von Neumann e de Harvard. Quais as vantagens e desvantagens de cada uma delas? Em relação aos equipamentos disponíveis no mercado atualmente (PCs, Notebooks, Video-Games, etc), indique um exemplo de equipamento e classifique em que tipo de arquitetura (Von Neumann ou Harvard) ele se enquadra.

- 2. Quais os principais componentes de uma arquitetura de computador do tipo Von Neumann? Dentre estes componentes, indique quais os elementos e propriedades (capacidade) de cada um que é usada para definir uma família/geração de microprocessadores (Exemplo: Intel 4004, Intel 8080, Intel 8086, Mostech 6502, Motorola 68000). Em outras palavras, "o que tem dentro de cada um destes processadores (componentes de uma Arquitetura de Von Neumann) que os caracteriza como pertencentes a uma família de processadores"?

- 3. Complete a tabela abaixo com os dados referentes a cada processador:

| Característica/Processador           | Neander* | Ramses* | 4004 | 6502 | Z80 | 8086 |

|--------------------------------------|----------|---------|------|------|-----|------|

| Fabricante                           |          |         |      |      |     |      |

| Dados (nro. de bits)                 |          |         |      |      |     |      |

| Endereços (nro. de bits)             |          |         |      |      |     |      |

| Clock                                |          |         |      |      |     |      |

| Nro. de Instruções                   |          |         |      |      |     |      |

| Flags disponíveis                    |          |         |      |      |     |      |

| Registradores                        |          |         |      |      |     |      |

| Modos diferentes de<br>Endereçamento |          |         |      |      |     |      |

| Tipos de E/S                         |          |         |      |      |     |      |

<sup>\*</sup> Neander e Ramses: Computadores hipotéticos definidos por Raul Weber no Livro "Fundamentos de Arquitetura de Computadores" (2001)

- 4. Quais os modos de endereçamento disponíveis no microprocessador Mostech 6502? Liste os modos de endereçamento do 6502, descrevendo as principais características de cada um deles, e dando um exemplo de instrução para cada um destes modos de endereçamento.

- 5. Em relação a ULA: como é obtido o Flag de Carry em operções da ULA de um processador? Quais as instruções típicas que afetam o Flag de Carry? Descreva um exemplo de aplicação em um programa onde o uso do Carry é necessário.

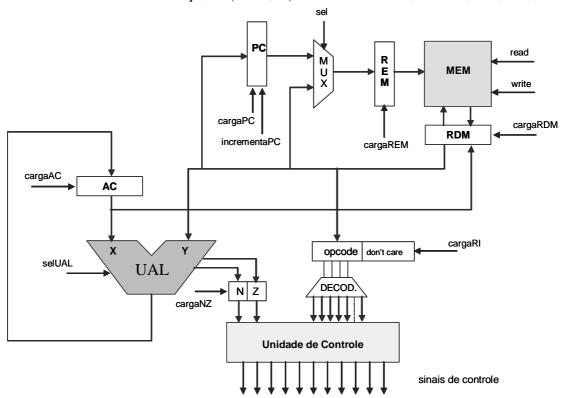

- 6. Em relação ao processador Neander: observe a figura abaixo que representa a arquitetura deste processador, e baseado nesta figura **descreva a execução passo-a-passo** da seguinte instrução, que se encontra armazenada no endereço \$06 (PC = \$06) da memória: LDA \$50 => \$06: \$20 \$50

- 7. Conforme o exercício acima (nro. 6), e baseado na mesma figura, **descreva a execução passo-a-passo** da seguinte instrução, que se encontra armazenada no endereço \$10 (PC = \$10) da memória de uma máquina baseada no processador do Neander: JZ \$40 => \$10: \$AO \$40

- 8. Considerando o processador Neander, é possível realizar uma adição de um valor de 16 bits? Se você considera que não é possível explique porque. Se você considera que é possível, explique como você faria esta operação.

- 9. Considerando um processador hipotético Ozorium (fictício), definido como um processador cujo registrador PC (Program Counter) possui 12 bits e cuja memória seja organizada em bancos de N posições de 12 bits (palavras de 12 bits). Qual seria o tamanho máximo da memória de programa que poderia se endereçar com este processador? Ou seja, quantas palavras de 12 bits poderiam ser armazenadas nesta memória?

- 10. Considerando novamente o processador hipotético Ozorium, e sabendo que suas instruções são também de 12 bits (RI Registrador de Instrução de 12 bits), qual o tamanho máximo do Conjunto de Instruções (Instruction Set) deste processador?

- 11. Defina e descreva as seguintes siglas e termos relacionados com a disciplina de Arquitetura de Computadores, relacionando em qual(is) componente(s) da Arquitetura de Von Neumann são usados:

- 1) Half-adder; 2) SR Latch, D Latch; 3) IR; 4) SP; 5) IRQ, INTR; 6) WR/RD Enable;

- 7) OPCode; 8) NOP; 9) BusRQ; 10) DMA; 11) Address Bus, Data Bus, Control Bus;

- 12) VLIW; 13) DRam, SRam; 14) EDVAC, IAS; 15) CLK.

- 12. Em relação a organização de memória, descreva a hierarquia de memórias em um computador, identificando a localização, principal função e características de cada tipo de memória.

- 13. O que é o *pipeline* de execução de uma instrução? Liste e descreva as principais etapas do ciclo de execução de uma instrução em uma CPU.

- 14. Quais são as operações internas (usualmente implementadas em micro-código) para a execução do ciclo de busca de uma instrução (Instruction Fetch)?

- 15. O que é o "pre-fetch" de uma instrução? Responda as questões abaixo sobre o pre-fetch de instruções:

- Qual o motivo de se realizar um pre-fetch de instruções em uma CPU?

- Qual a principal vantagem? Quais as desvantagens e/ou problemas associados ao pre-fetch?

- O que são os estágios do pipeline de instrução e em que etapas o pré-fetch pode ser útil?

- Porque o esvaziamento do pipeline (branch) pode ser um problema para o pré-fetch?

- Quais as possíveis soluções para tratar os desvios (branchs) em um processador que se utiliza da técnica de pre-fetch de instruções?

- O que é o "branch prediction"?

- 15. O que é uma memória cache? Responda as questões abaixo sobre a memória cache:

- Qual o motivo de se ter uma memória cache em um processador?

- O que é o cache de instruções de um processador?

- Qual a vantagem de se ter uma memória cache para acesso aos dados da memória principal? Quais as desvantagens e/ou problemas associados ao uso de uma memória cachê?

- 16. Quais são os principais modos (métodos) de E/S usados em uma computador tradicional (cite os 3 principais)? Descreva cada um deles, indicando suas principais características, vantagens e desvantagens.

- 17. Quais são os principais modos disponíveis em um processador (cite os 2 modos usuais), em termos de comandos, usados para a realização de E/S?

- 18. Os processadores mais modernos estudados na disciplina, como o 6502, Z80, 8086 e 68000, são caracterizados por transições em termos de sua capacidade de armazenamento de dados e instruções. Em relação ao barramentos de dados e endereços e registradores internos, qual era a capacidade (nro. de bits) de cada um destes processadores? [Preencher a tabela abaixo]

| Nro. de Bits           | 6502 | Z80 | 8088 | 8086 | 68000 |

|------------------------|------|-----|------|------|-------|

| Barramento de Dados    |      |     |      |      |       |

| Barramento de End.     |      |     |      |      |       |

| Registrador PC         |      |     |      |      |       |

| Registrador Acumulador |      |     |      |      |       |

19. O que significa dizer que os processadores Intel 8080, Intel 8085 e Z80 são "byte code compatible"? Qual a relação entre os processadores 8080 e 8085 da Intel com seu sucessor 8088/8086 em relação ao conjunto de instrucões?

- 20. Quais as principais melhorias introduzidas no processador Zilog Z80 em relação ao Intel 8080? Qual o impacto destas melhorias em termos de desenvolvimento de programas?

- 21. Em relação ao "momento histórico" de migração dos processadores de 8/16 bits como o 6502, 8080 e Z80 para os processadores de 16/32 bits como o 68000 e o 80x86, como você explica o sucesso da Intel com os processadores 8088/8086 que vieram a dominar o mercado de microprocessadores? O que levou ao sucesso destes processadores e seu domínio sobre outros processadores lançados no mercado na mesma época?

- 22. Porque a arquitetura do processador Intel 8086 é considerada um "Frankenstein"? Como funciona o esquema de endereçamento adotado pelo 8086 para acesso a dados e instruções na memória? Qual a relação entre os registradores internos (16 bits CS/IP) e o barramento externo de endereços (20 bits)? Explique de modo detalhado como funciona este esquema de endereçamento, com exemplos.

- 23. Quais as principais características dos processadores da família 80x86 que caracterizam a evolução desta família de processadores? [8088, 8086, 80286, 80386, 80486, Pentium]

- 24. Qual foi o grande marco da década de 80, uma revolução na arquitetura dos processadores, que abalou de certa forma a dominância dos processadores Intel sobre os demais? Qual nova tecnologia surgiu vinda das Universidades nesta década e que apresentava uma proposta capaz de "desafiar" o domínio da Intel sobre o mercado?

- 25. Enumere pelo menos 3 tecnologias relacionadas à arquitetura dos processadores que permitiram melhorar significativamente o desempenho dos microprocessadores comerciais.

### [Arquiteturas Modernas / Avançadas]

Continua na Lista de Exercícios 2 ©

#### [Questões de Programação]

- Faça um programa em linguagem de montagem para o 6502 para adicionar 2 valores de 16 bits.

O programa deve iniciar sua execução no endereço \$1000 da memória, e os dados devem estar armazenados nos endereços \$2000 (MSB) e \$2001 (LSB) para o Valor1 e \$2002 (MSB) e \$2003 (LSB) para o Valor2. O resultado deve ser armazenado no endereço \$3000 (MSB) e \$3001 (LSB).

MSB = Most Significative Byte / LSB = Least Significative Byte

- 2. Faça um programa em linguagem de montagem para o 6502 para subtrair 2 valores de 16 bits. O programa deve iniciar sua execução no endereço \$0500 da memória, e os dados devem estar armazenados na pilha (stack). O Valor2 (16 bits) deve ser subtraído do Valor1 (16 bits). O Valor1 está armazenado em baixo na pilha, com o MSB mais acima na pilha e o LSB mais abaixo na pilha. O Valor2 está armazenado no topo da pilha, acima do Valor2, com o MSB mais acima na pilha e o LSB mais abaixo na pilha. O resultado deve ser armazenado no endereço \$1000 (MSB) e \$1001 (LSB). MSB = Most Significative Byte / LSB = Least Significative Byte

- 3. Faça um programa em linguagem de montagem para o 6502. Considere que existe uma função de I/O mapeado em memória para escrita na tela do *display* do computador. O display é capaz de exibir até 32 caracteres, onde basta escrever na memória de I/O o código ASCII, escrevendo assim o caracter nos endereços correspondentes a cada posição do display. O endereço de base do display é \$E000 (primeiro caracter), sendo que o último caracter do display está mapeado na posição \$E01F. Faça um programa que escreva a mensagem "Hello world!" na tela do display.

- 4. Faça um programa em linguagem de montagem para o 6502, baseado no programa anterior. Faça uma sub-rotina que exiba a mensagem "Hello world!" e uma outra subrotina que limpe o visor do display, ou seja, escreva espaços em branco em todas as 32 posições do display. Faça um programa exiba a mensagem "hello" de modo que esta fique piscando na tela de display. O programa deve alternar entre exibir a mensagem "hello", pausar (delay) um certo tempo, limpar o display, pausar um certo tempo, e repetir o ciclo novamente (mensagem, pausa, limpa, pausa) de modo indefinido. Observações:

- O programa deve ser composto de pelo menos 3 sub-rotinas (exibe mensagem, limpa tela, pausa);

- A rotina de pausa pode ser implementada com um grande "loop" de instruções que não fazem nada (faça um contador que repita a execução do laço de instruções "gasta tempo" como o NOP).

- 5. Considerando o material de aula descrevendo as características do processador Z80 (registradores), e o conjunto de instruções disponibilizado na Internet (ver página de "Material de Aulas" na Wiki e em "Material Complementar" nesta página), implemente os programas acima de 1 a 4 usando o processador Z80 como base (Z80 Instruction Set).

| FIM |  |

|-----|--|

|     |  |