### Introduction to VHDL

Prof. Vanderlei Bonato - <a href="mailto:vbonato@icmc.usp.br">vbonato@icmc.usp.br</a>

# Summary

- History

- VHDL Structure

- Sequencial and Parallel Execution

- Signal and Variable

- Data Types, Assignments, Data Conversions

- Operators

- Component Instantiation

- Bi-directional Pins

- Exercises

### **Concepts**

- VHDL is the VHSIC (Very High Speed Integrated Circuit) Hardware Description Language

- VHDL is an international standard specification language for describing digital hardware used by industry worldwide

- VHDL enables hardware modeling from the gate to system level

- VHDL provides a mechanism for digital design and reusable design documentation

## **History of VHDL**

- Launched in 1980

- Aggressive effort to advance state of the art

- Object was to achieve significant gains in VLSI technology

- Need for common descriptive language

- In July 1983, a team of Intermetrics, IBM and Texas Instruments were awarded a contract to develop VHDL

## **History of VHDL**

- In August 1985, the final version of the language under government contract was released: VHDL Version 7.2

- In December 1987, VHDL became IEEE Standard 1076-1987 and in 1988 an ANSI approved standard

- In September 1993, VHDL was restandardized to clarify and enhance the language (IEEE Standard 1076-1993)

- Since then there has been many other VHDL standard revision

### **How about Quartus II**

- The Quartus II software supports a subset of the constructs defined by the IEEE Std 1076-1987, and IEEE Std 1076-1993, and IEEE Std 1076-2008

- It supports only those constructs that are relevant to logic synthesis

- The Quartus II 11.1 software contains support for VHDL 2008: IEEE Std 1076-2008

- The Quartus II software also supports the packages defined by these patterns

# Why Use VHDL?

- Provides technology independence

- Describes a wide variety of digital hardware

- Eases communication through standard language

- Allows for better design management

- Provides a flexible design language

### **VHDL Design Process**

- Problem: design a single bit half adder with carry and enable

- Specifications

- Passes results only on enable high

- Passes zero on enable low

- Result gets x plus y

- Carry gets any carry of x plus y

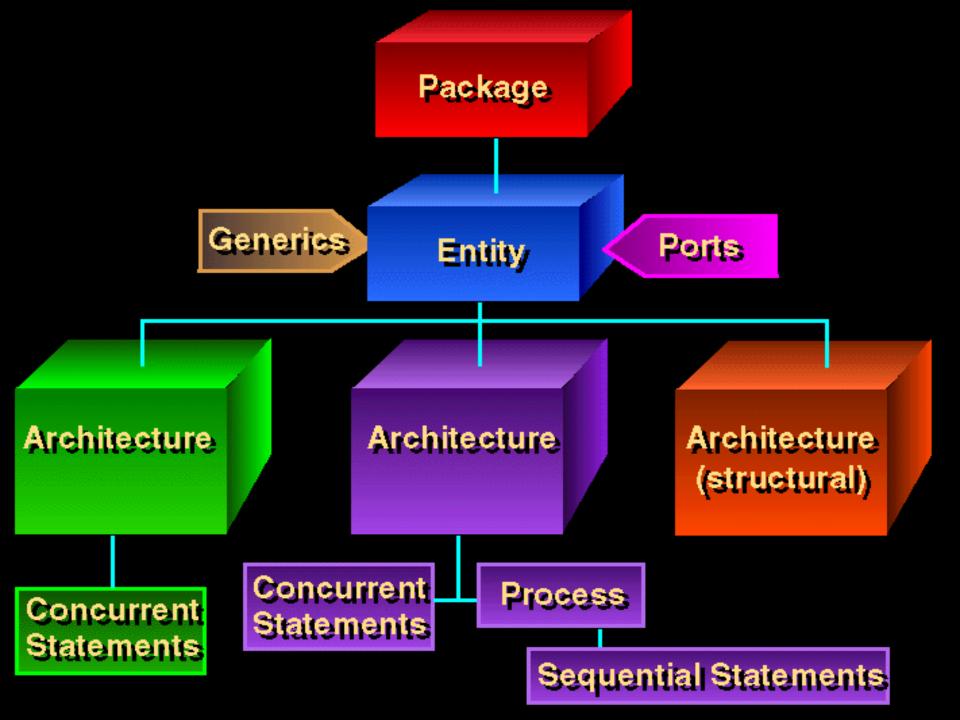

## **Entity Declaration**

- An entity declaration describes the interface of the component

- PORT clause indicates input and output ports

- An entity can be thought of as a symbol for a component

- Generics may be added for readability, maintenance and configuration

### **Entity Declaration**

### **Architecture Declaration**

Architecture declarations describe the operation of the component

Many architectures may exist for one entity, but only one may be active at a time

An architecture is similar to a schematic of the component

```

ARCHITECTURE behavior1 OF

half adder IS BEGIN

PROCESS (enable, x, y)

BEGIN

carry

enable

IF (enable = '1') THEN

result

result <= x XOR y;

carry <= x AND y;

ELSE

carry <= '0'

result <= '0';

END PROCESS;

END behavior1;

```

### Packages and Libraries

- User defined constructs declared inside <u>architectures</u> and <u>entities</u> are not visible to other entities

- Subprograms, user defined data types, and constants can not be shared

- Packages and libraries provide the ability to reuse constructs in multiple entities and architectures

- An important VHDL library is the IEEE library. This

package provides a set of user-defined datatypes

and conversion functions that should be used in

VHDL designs.

- LIBRARY ieee;

- USE ieee.std\_logic\_1164.ALL;

### **Sequential and Concurrent Statements**

- VHDL provides two different types of execution: sequential and concurrent

- Different types of execution are useful for modeling of real hardware

- Supports various levels of abstraction

- Sequential statements view hardware from a "programmer" approach

- Concurrent statements are order-independent and asynchronous

### **Sequential Statements**

Sequential statements run in top to bottom order

Sequential execution most often found in behavioral descriptions

Statements inside PROCESS execute sequentially

### **Concurrent Statements**

- All concurrent statements occur simultaneously

- How are concurrent statements processed?

- Simulator time does not advance until all concurrent statements are processed

- Some concurrent statements

- Block, process, assert, signal assignment, procedure call, component instantiation

### **VHDL Processes**

- Assignments executed sequentially

- Sequential statements

- {Signal, variable} assignments

- Flow control

- if <condition> then <statements> else <statements> end if;

- <u>for</u> <range> loop <statements> end loop;

<u>while</u> <condition> loop <statements> end loop;

- case < condition > is when < value > = > < statements >;

when < value > = > < statements >;

when others = > < statements >;

end case;

- Wait on <signal> until <expression> for <time>;

- <u>Assert</u> <condition> report <string> severity <level>;

### **VHDL Processes**

A VHDL process statement is used for all behavioral descriptions

```

[process label :] PROCESS

[(sensitivity list)]

process declarations

BEGIN

process statements

END PROCESS [process label];

```

### Process Example - Carry Bit

```

Carry: PROCESS (A, B, Cin)

BEGIN

IF (A = '1' and B = '1') THEN

Cout <= '1';

ELSIF (A = '1' \text{ and } Cin = '1') THEN

Cout <= '1';

ELSIF (B = '1' and Cin = '1') THEN

Cout <= '1';

ELSE

Cout <= '0';

END IF;

END PROCESS Carry;

```

# A Design Example: 8-bits Register with asynchronous clear

```

LIBRARY ieee;

USE ieee.std logic 1164.all;

ENTITY reg8 IS

PORT (clock, rst : IN BIT;

D: IN STD LOGIC VECTOR (7 DOWNTO 0);

Q: OUT STD LOGIC VECTOR (7 DOWNTO 0));

END reg8;

ARCHITECTURE behavior OF reg8 IS

BEGIN

register8: PROCESS (clock,rst)

BEGIN

IF rst = '0' THEN

0 <= "0000000";</pre>

ELSIF clock'EVENT AND clock ='1' THEN

O \leq D;

END IF;

END PROCESS register8;

END behavior;

```

### A Design Example: 2-bits Counter

```

ENTITY count2 IS

PORT (clock : IN BIT;

q1, q0: OUT BIT);

END count2:

ARCHITECTURE behavior OF count2 IS

BEGIN

count up: PROCESS (clock)

VARIABLE count value: NATURAL := 0;

BEGIN

IF clock='1' THEN

count value := (count value+1) MOD 4;

q0 <= bit'val(count value MOD 2);

q1 <= bit'val(count value/2);</pre>

END IF;

END PROCESS count up;

END behavior:

```

### Signals vs Variables

#### Variables

- Used for local storage of data

- Generally not available to multiple <u>components</u> and <u>processes</u>

- All variable assignments take place immediately

- Variables are more convenient than signals for the storage of data

- Variables may be made global

### Signals

- Used for communication between <u>components</u>

- Signals can be seen as <u>real</u>, <u>physical</u> signals

- Some delay must be incurred in a signal assignment

## **Assignments**

```

ARCHITECTURE test1 OF

ARCHITECTURE test2 OF test mux IS BEGIN

test mux IS

SIGNAL a : BIT := '1'; PROCESS (result)

VARIABLE a : BIT := '1';

SIGNAL b : BIT := '0';

VARIABLE b : BIT := '0';

BEGIN

BEGIN

...more statements...

...more statements...

a := b;

a \le b;

b := a;

b <= a;

...more statements...

...more statements...

END PROCESS;

END test2;

END test1;

```

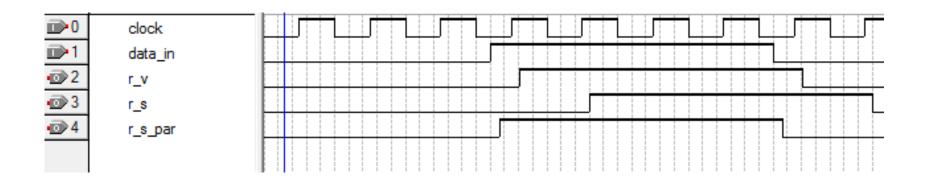

### Signal x Variable Behaviour

```

ENTITY aulayhdl IS

PORT (clock, data_in : IN BIT;

r_v, r_s, r_s_par: OUT BIT);

END aulavhdl;

ARCHITECTURE behavior OF aulayhdl IS

signal a_s, a_s_par: BIT := '0';

BEGIN

PROCESS (clock)

variable a v: BIT := '0';

BEGIN

IF clock='1' THEN

a v := data in;

r v \le a v;

a_s <= data in;

r s \le a s;

END IF;

END PROCESS;

a_s_par <= data_in;

r_s_par <= a_s_par;

END behavior;

```

## Signal x Variable Behaviour

- Percebam a diferença de comportamento do "signal" dentro e fora do processo!

- Quanto a "variable" não há surpresa, pois é utilizada somente dentro do processo

# **Data Types**

| Data types                    | Synthesizable values                        |

|-------------------------------|---------------------------------------------|

| BIT, BIT_VECTOR               | '0', '1'                                    |

| STD_LOGIC, STD_LOGIC_VECTOR   | 'X', '0', '1', 'Z' (resolved)               |

| STD_ULOGIC, STD_ULOGIC_VECTOR | 'X', '0', '1', 'Z' (unresolved)             |

| BOOLEAN                       | True, False                                 |

| NATURAL                       | From 0 to $+2$ , 147, 483, 647              |

| INTEGER                       | From $-2,147,483,647$ to $+2,147,483,647$   |

| SIGNED                        | From $-2,147,483,647$ to $+2,147,483,647$   |

| UNSIGNED                      | From 0 to $+2,147,483,647$                  |

| User-defined integer type     | Subset of INTEGER                           |

| User-defined enumerated type  | Collection enumerated by user               |

| SUBTYPE                       | Subset of any type (pre- or user-defined)   |

| ARRAY                         | Single-type collection of any type above    |

| RECORD                        | Multiple-type collection of any types above |

# **Dealing with Data Types**

```

TYPE byte IS ARRAY (7 DOWNTO 0) OF STD LOGIC;

-- 1D

-- array

TYPE mem1 IS ARRAY (0 TO 3, 7 DOWNTO 0) OF STD LOGIC;

-- 2D

-- array

TYPE mem2 IS ARRAY (0 TO 3) OF byte;

-- 1Dx1D

-- array

TYPE mem3 IS ARRAY (0 TO 3) OF STD LOGIC VECTOR(0 TO 7); -- 1Dx1D

-- array

-- scalar signal

SIGNAL a: STD LOGIC;

-- scalar signal

SIGNAL b: BIT;

-- 1D signal

SIGNAL x: byte;

SIGNAL y: STD LOGIC VECTOR (7 DOWNTO 0);

-- 1D signal

SIGNAL v: BIT_VECTOR (3 DOWNTO 0);

-- 1D signal

SIGNAL z: STD LOGIC VECTOR (x'HIGH DOWNTO 0);

-- 1D signal

SIGNAL w1: mem1;

-- 2D signal

-- 1Dx1D signal

SIGNAL w2: mem2;

-- 1Dx1D signal

SIGNAL w3: mem3;

```

## **Scalar Assignments**

# **Vector Assignments**

```

x <= "111111110";

y \le ('1','1','1','1','1','1','0','Z');

z <= "11111" & "000";

x \ll (OTHERS => '1');

y \le (7 = > '0', 1 = > '0', OTHERS = > '1');

z \ll y;

y(2 DOWNTO 0) \le z(6 DOWNTO 4);

w2(0)(7 DOWNTO 0) <= "11110000";

w3(2) \le y;

z \le w3(1);

z(5 \text{ DOWNTO } 0) \le w3(1)(2 \text{ TO } 7);

w3(1) \le "00000000";

w3(1) \le (OTHERS => '0');

w2 <= ((OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0'),(OTHERS=>'0'));

(OTHERS=>'0'), (OTHERS=>'0'));

w1 <= ((OTHERS=>'Z'), "11110000", "11110000", (OTHERS=>'0'));

```

### **llegal Assignments**

```

----- Illegal scalar assignments: ------

-- type mismatch (BIT x STD_LOGIC)

b \le a;

w1(0)(2) \le x(2); -- index of w1 must be 2D

w2(2,0) \le a;

-- index of w2 must be 1Dx1D

----- Illegal array assignments: -----

-- type mismatch

x \le y;

y(5 \text{ TO } 7) \le z(6 \text{ DOWNTO } 0);

-- wrong direction of y

w1 \le (OTHERS => '1');

-- w1 is a 2D array

w1(0, 7 DOWNTO 0) \le "1111111111"; -- w1 is a 2D array

w2 \ll (OTHERS => 'Z');

-- w2 is a 1Dx1D array

w2(0, 7 DOWNTO 0) <= "11110000"; -- index should be 1Dx1D

```

### **DOWNTO** and **TO**

```

SIGNAL x: BIT;

-- x is declared as a one-digit signal of type BIT.

SIGNAL y: BIT VECTOR (3 DOWNTO 0);

-- y is a 4-bit vector, with the leftmost bit being the MSB.

SIGNAL w: BIT VECTOR (0 TO 7);

-- w is an 8-bit vector, with the rightmost bit being the MSB.

x \le '1':

-- x is a single-bit signal (as specified above), whose value is

-- '1'. Notice that single quotes (' ') are used for a single bit.

y \le "0111";

-- y is a 4-bit signal (as specified above), whose value is "0111"

-- (MSB='0'). Notice that double quotes (" ") are used for

-- vectors.

w \le "01110001";

-- w is an 8-bit signal, whose value is "01110001" (MSB='1').

```

### **Bit Levels**

- BIT (and BIT\_VECTOR): 2-level logic ('0', '1')

- STD\_LOGIC (and STD\_LOGIC\_VECTOR): 8-valued logic system introduced in the IEEE 1164 standard.

```

Ϋ́,

Forcing Unknown

(synthesizable unknown)

(synthesizable logic '1')

·0'

Forcing Low

Forcing High

'1'

(synthesizable logic '0')

ʻZ'

High impedance

(synthesizable tri-state buffer)

'W'

Weak unknown

'L'

Weak low

'H'

Weak high

```

٠\_,

Don't care

Most of the std\_logic are intended for simulation only!

### **ULOGIC**

- STD\_ULOGIC (STD\_ULOGIC\_VECTOR): 9-level logic system introduced in the IEEE 1164 standard ('U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-').

- STD\_LOGIC system described above is a subtype of STD\_ULOGIC. The latter includes an extra logic value, 'U', which stands for unresolved. Thus, contrary to STD\_LOGIC, conflicting logic levels are not automatically resolved here, so output wires should never be connected together directly. However, if two output wires are never supposed to be connected together, this logic system can be used to detect design errors.

### SIGNED and UNSIGNED

- Their syntax similar to STD\_LOGIC\_VECTOR

- SIGNED and UNSIGNED are intended mainly for arithmetic operations

- Logic operations are not allowed

```

SIGNAL x: SIGNED (7 DOWNTO 0);

SIGNAL y: UNSIGNED (0 TO 3);

```

### **Data Conversion**

- VHDL does not allow direct operations between data of different types

- Conversions are necessary

- Several data conversion functions can be found in the std\_logic\_arith package of IEEE library

### std\_logic\_arith Conversion Functions

- conv\_integer(p): Converts a parameter p of type INTEGER, UNSIGNED, SIGNED, or STD\_ULOGIC to an INTEGER value. Notice that STD\_LOGIC\_ VECTOR is not included.

- conv\_unsigned(p, b): Converts a parameter p of type INTEGER, UNSIGNED,

SIGNED, or STD\_ULOGIC to an UNSIGNED value with size b bits.

- conv\_signed(p, b): Converts a parameter p of type INTEGER, UNSIGNED,

SIGNED, or STD\_ULOGIC to a SIGNED value with size b bits.

- conv\_std\_logic\_vector(p, b): Converts a parameter p of type INTEGER, UN-SIGNED, SIGNED, or STD\_LOGIC to a STD\_LOGIC\_VECTOR value with size b bits.

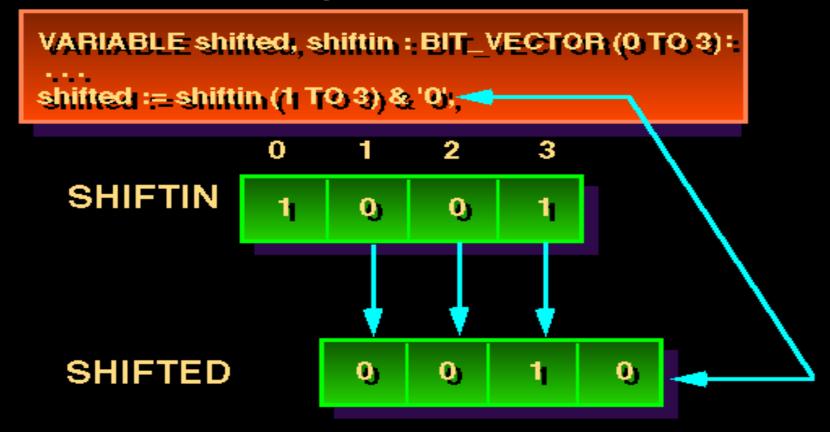

# **Operators**

| Operator type | Operators                                     | Data types                                                                        |

|---------------|-----------------------------------------------|-----------------------------------------------------------------------------------|

| Assignment    | <=, :=, =>                                    | Any                                                                               |

| Logical       | NOT, AND, NAND,<br>OR, NOR, XOR, XNOR         | BIT, BIT_VECTOR,<br>STD_LOGIC, STD_LOGIC_VECTOR,<br>STD_ULOGIC, STD_ULOGIC_VECTOR |

| Arithmetic    | $+, -, *, /, **$ (mod, rem, abs) $^{\bullet}$ | INTEGER, SIGNED, UNSIGNED                                                         |

| Comparison    | =, /=, <, >, <=, >=                           | All above                                                                         |

| Shift         | sll, srl, sla, sra, rol, ror                  | BIT_VECTOR                                                                        |

| Concatenation | &, (,,,)                                      | Same as for logical operators, plus SIGNED and UNSIGNED                           |

### The concatentation operator &

### The exponentiation operator \*\*

```

x_i := 5^{**}5, --- 5^{5}, QK

y_i := 0.5^{**}3, --- 0.5^{5}, QK

x_i := 4^{**}0.5, --- 4^{5}0.5, bad

y_i := 0.5^{**}(-2), --- 0.5^{5}(-2), QK

```

# Component instantiation (Structural VHDL)

```

component fifo cam is

port(

data

: in STD_LOGIC_VECTOR (31 downto 0);

: in STD LOGIC;

wrreq

: in STD LOGIC;

rdreq

: in STD LOGIC;

rdclk

: in STD LOGIC;

wrclk

: in STD LOGIC;

aclr

: out STD LOGIC VECTOR (31 downto 0);

q

rdempty

: out STD LOGIC;

: out STD LOGIC );

wrfull

end component;

```

fifo: fifo\_cam port map(pixel,'1',read\_cs,clk\_n,ready\_pixel,aclr\_fifo,readdata,waitrequest,fifofull);

## Bidirectional pin

```

ENTITY proc eld2 is

PORT(clk, rst

: in STD LOGIC;

data

: inout STD LOGIC VECTOR(7 downto 0);

: buffer STD LOGIC;

web oeb

address

: out STD_LOGIC_VECTOR(7 downto 0);

: out STD LOGIC VECTOR(7 downto 0);

pc out, ir out

: out STD_LOGIC_VECTOR(2 downto 0)

saida

END proc eld2;

signal ACC : std logic vector(7 downto 0);

web oeb <= '1'; --1 escreve e 0 lê da mem.

data <= ACC WHEN web oeb='1' else "ZZZZZZZZZ";

web oeb <= '0'; --1 escreve e 0 lê da mem.

ACC <= data;

```

### **Tips**

The ENTITY name and the file name must be the same

- Physical and time data types are not synthesizable for FPGAs

- ohm, kohm

- fs, ps, ns, um, ms, min, hr

### And more ...

### Function

- Produce a single return value

- Requires a RETURN statement

#### Procedure

- Produce many output values

- Do not require a RETURN statement

### Testbench

- Generate stimulus for simulation

- Compare output responses with expected values

# Implemente em VHDL os seguintes componentes

- FFs do tipo D, T e JK

- Registrador de deslocamento da direita para a esquerda

- Conversor de binário para display de 7 segmentos

- Crie um componente somador completo de 1 bit e instancie esse mesmo componente para formar um somador/subtrator de 8 bits do tipo ripple-carry. Considere que os números estão em complemento de 2; e para o controle da operação utilize C=0 para adição e C=1 para subtração. Indique também overflow. Utilize STD\_LOGIC\_VECTOR para os sinais de entrada e saída

### References

Pedroni, Volnei A. Circuit Design with VHDL, MIT Press, 2004

- DARPA/Tri-Services RASSP Program

- http://www.vhdl.org/rassp/

- Brown, S. and Vranesic, Z.. Fundamentals of Digital Logic with VHDL Design, 2<sup>nd</sup> Ed., P. 939, 2005.