Universidade de São Paulo - São Carlos,SP

Instituto de Ciências Matemáticas e de Computação

USP - ICMC - SSC SSC 0610 - Eng. Comp. - 20. Semestre 2010

# Disciplina de Organização de Computadores I

**Prof. Fernando Santos Osório**

Email: fosorio [at] { icmc. usp. br , gmail. com } Página Pessoal: http://www.icmc.usp.br/~fosorio/

Estagiário PAE Maurício Dias - Email: macccdias [at] gmail.com

Material on-line Wiki ICMC - http://wiki.icmc.usp.br/index.php/Ssc-610

Aula 08q

gosto 2010

### Aula 06 - Tópicos Abordados

#### Conteúdos Abordados:

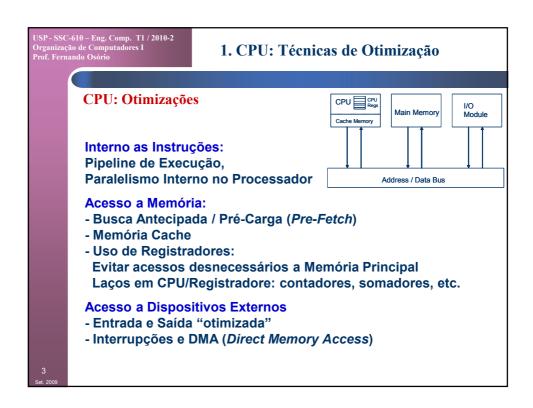

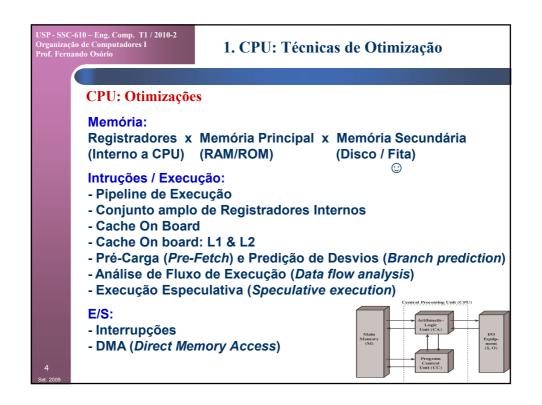

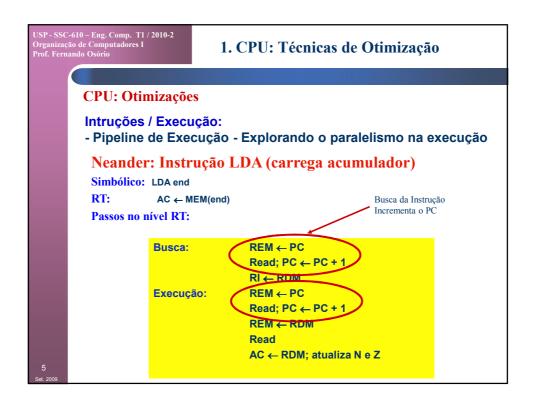

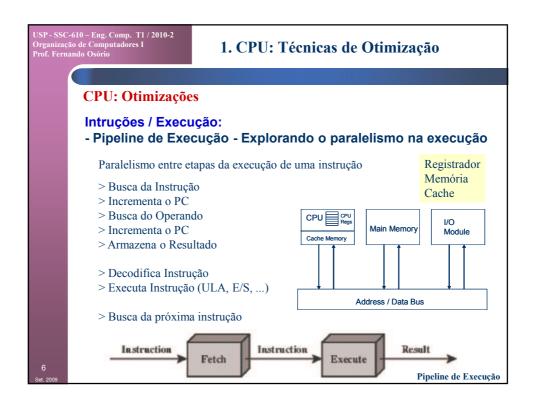

- 1. CPU: Técnicas de Otimização

- > Técnicas de Pipeline

- > Pré-Fetch de Instrução

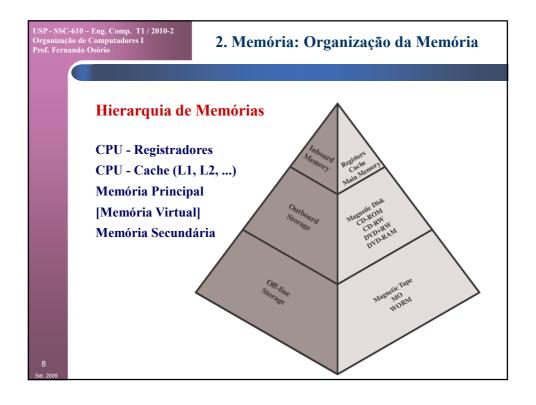

- 2. Memória Organização da Memória

- > Hierarquia de Memória

- > Registradores

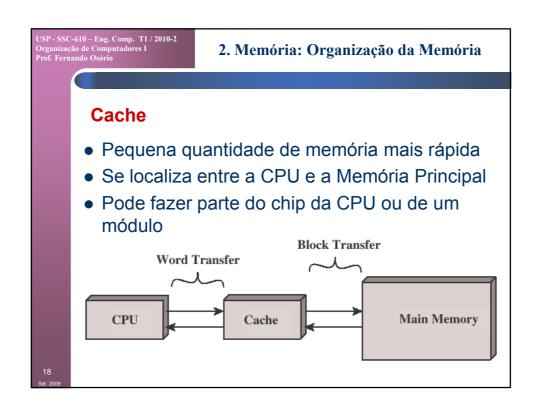

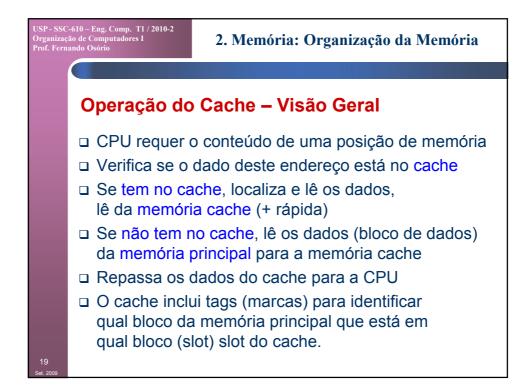

- > Memória Cache

- > Memória Principal

- > Memória Secundária

- > Memória Virtual

2

Z -1. 2022

· SSC-610 – Eng. Comp. T1 / 2010-2 nização de Computadores I Fernando Osório

2. Memória: Organização da Memória

### **Performance**

- Tempo de Acesso / Access time

- Tempo entre apresentar o endereço e obter o dado válido.

- Ciclo de Memória / Memory Cycle time

- Tempo que pode ser necessário para a memória se "recuperar" antes de um próximo acesso.

- Tempo de ciclo = access + recovery

- Taxa de Transferência / Transfer Rate

- Taxa na qual os dados são movidos.

2. Memória: Organização da Memória

## **Tipos Físicos de Memórias**

- Semicondutor

- RAM (SRAM, DRAM), ROM, Flash

- Magnética

- Disco e Fita

- Ótica

- CD & DVD

- Outros

- Bubble memory

- Holográfica

USP - SSC-610 – Eng. Comp. T1 / 2010-2 Organização de Computadores I

### 2. Memória: Organização da Memória

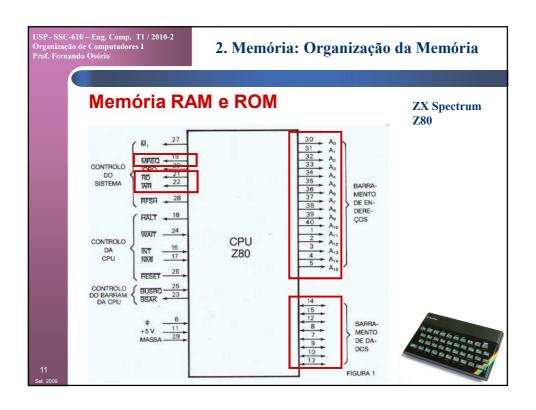

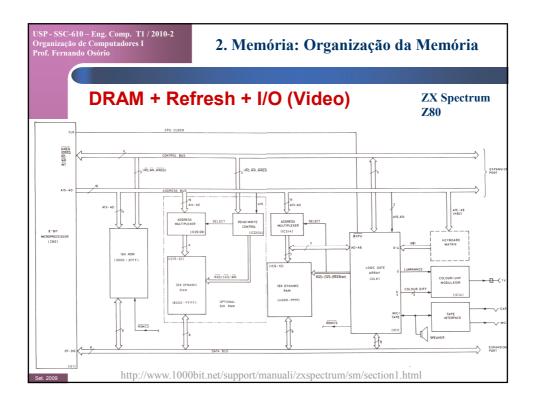

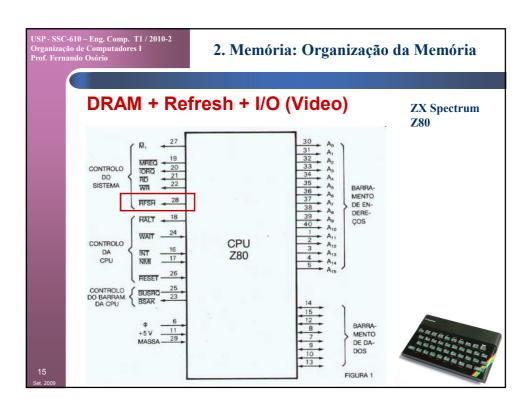

# DRAM + Refresh + I/O (Video)

ZX Spectrum Z80

### **Dynamic Memory Refresh**

The CPU incorporates built-in **dynamic RAM refresh circuitry**. As part of the instruction OP code fetch cycle, the CPU performs a memory request after first placing the refresh address on the lower eight bits of the address bus. At the end of the cycle the address is incremented so that over 255 fetch cycles, each row of the dynamic RAM is refreshed.

This mechanism only applies to the optional 32k expansion RAM in the the 48k Spectrum. An alternative refresh method is adapted for the standard 16k RAM.

### **MEMORY ORGANISATION**

In the standard 16k Spectrum there are 32k bytes of addressable memory equally divided between **ROM** and **RAM**.

The lower 16k bytes of memory (addresses 0000 - 3FFF) are implemented in a ROM (IC5) which holds the monitor program. This program is a complex Z80 machine code program divided broadly into three parts one each covering the input/output routines, the BASIC interpreter and expression handling.

The upper 16 bytes of memory (addresses 4000 - 7FFF) are implemented using eight 16k bit dynamic RAMs (IC6-IC13). Approximately half of this space is available to the user for writing BASIC or machine code programs.

The remainder is used to hold the system variables including 6k bytes reserved for the memory mapped **display area**.

14 let. 2009

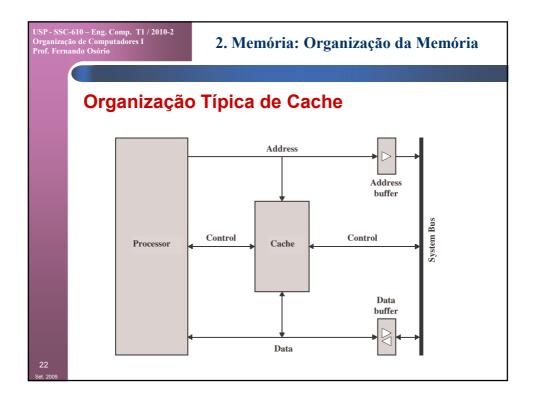

Projeto do Cache

Tamanho

Função de Mapeamento

Algoritmo de Atualização

Política de escrita

Tamanho do bloco

Número de caches

USP - SSC-610 – Eng. Comp. T1 / 2010-2 Organização de Computadores I Prof. Fernando Osório

2. Memória: Organização da Memória

### Size does matter ("Tamanho faz diferença")

- Custo

- O custo de ter mais memória de cache é elevado.

- Velocidade

- Mais cache => Mais rápido (até certo ponto);

- Verificar os dados presentes no cache consome um certo tempo.

21 Set 2009

USP - SSC-610 – Eng. Comp. T1 / 2010-2 Organização de Computadores I Prof. Fernando Osório

### INFORMAÇÕES SOBRE A DISCIPLINA

USP - Universidade de São Paulo - São Carlos, SP

ICMC - Instituto de Ciências Matemáticas e de Computação

SSC - Departamento de Sistemas de Computação

Prof. Fernando Santos OSÓRIO

Web institucional: http://www.icmc.usp.br/ssc/ Página pessoal: http://www.icmc.usp.br/~fosorio/

E-mail: fosorio [at] icmc. usp. br ou fosorio [at] gmail. com

Disciplina de Organização de Computadores I / Eng. Comp.

Estagiário PAE: Maurício A. Dias

Web disciplina: http://wiki.icmc.usp.br/index.php/Ssc-610

> Programa, Material de Aulas, Critérios de Avaliação,

> Lista de Exercícios, Trabalhos Práticos, Datas das Provas

∠3 Agosto 20