Mudanças entre as edições de "SSC-109(bonato) 2017"

De CoteiaWiki

| Linha 32: | Linha 32: | ||

* Manual DE0-CV: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE0-CV/DE0_CV_User_Manual.pdf | * Manual DE0-CV: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE0-CV/DE0_CV_User_Manual.pdf | ||

* Manual DE2-115: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE2-115/DE2_115_User_Manual.pdf | * Manual DE2-115: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE2-115/DE2_115_User_Manual.pdf | ||

| + | |||

| + | * Trabalho Final | ||

| + | ** Descrição: [[Arquivo:SSC0109_2017_1_TF.pdf]] | ||

| + | ** Aplicativo evaluator: em breve! | ||

| + | ** Grupos: | ||

| + | *** | ||

==Avisos== | ==Avisos== | ||

| Linha 39: | Linha 45: | ||

<span style="background:#FF0000">'''ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO'''</span> | <span style="background:#FF0000">'''ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO'''</span> | ||

| + | * '''DESCRIÇÃO DO TRABALHO JÁ DISPONÍVEL NA SEÇÃO ARQUIVOS!''' | ||

* '''Terça-feira 06/06 e quinta-feira 15/06 não haverá aula!!!!!''' | * '''Terça-feira 06/06 e quinta-feira 15/06 não haverá aula!!!!!''' | ||

| − | |||

* '''Link para decidir horário de monitoria: http://doodle.com/poll/aiumykxu9x3ppcxa''' | * '''Link para decidir horário de monitoria: http://doodle.com/poll/aiumykxu9x3ppcxa''' | ||

* Datas importantes: | * Datas importantes: | ||

Edição das 21h43min de 3 de junho de 2017

Índice

SSC-109 - PRÁTICA EM LÓGICA DIGITAL - 2017/1

Prof. Vanderlei Bonato (PRÁTICA)

E-mail: vbonato@usp.br

Estagiário PAE: André Bannwart Perina

E-mail: abperina@usp.br

Monitor: Ítalo Tobler Silva

E-mail: italo.ts4895@gmail.com

Monitor (quinta): Allan Domingues

Horário de atendimento: Qua (15:00 - 17:00) e Qui (13:00 - 14:00)

E-mail: allan.domingues@usp.br

FAQ

Para dúvidas frequentes relacionadas à instabilidade emocional do Quartus/ModelSim:

Arquivos

- Descrição da disciplina: Arquivo:ApresentacaoCursoSSC0109.pdf

- Pin mapping DE0-CV: Arquivo:DE0 CV Main Pins.zip

- Pin mapping DE2-115: Arquivo:DE2 115 Main Pins.zip

- Manual DE0-CV: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE0-CV/DE0_CV_User_Manual.pdf

- Manual DE2-115: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE2-115/DE2_115_User_Manual.pdf

- Trabalho Final

- Descrição: Arquivo:SSC0109 2017 1 TF.pdf

- Aplicativo evaluator: em breve!

- Grupos:

Avisos

As notas da prova prática já estão no ar!

ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO

- DESCRIÇÃO DO TRABALHO JÁ DISPONÍVEL NA SEÇÃO ARQUIVOS!

- Terça-feira 06/06 e quinta-feira 15/06 não haverá aula!!!!!

- Link para decidir horário de monitoria: http://doodle.com/poll/aiumykxu9x3ppcxa

- Datas importantes:

- Prova prática: 09/05 (turma de terça) 11/05 (turma de quinta)

- Trabalho prático principal: 27/06 (turma de terça) 29/06 (turma de quinta)

ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO ATENÇÃO

Notas

- Prova Prática:

- Terça 16h: Arquivo:SSC0109 2017 1 1.pdf

- Quinta 14h: Arquivo:SSC0109 2017 1 4.pdf

- Quinta 16h: Arquivo:SSC0109 2017 1 2.pdf

Método de avaliação

Para mais detalhes ver arquivo de descrição da disciplina.

- 20% atividades

- 30% prova prática

- 50% trabalho prático principal

Trabalho Final

Em breve...

Cronograma realizado

- (Ter. 14/03 - Qui. 16/03): Aula 01: Introdução do curso, apresentação da ementa, critério de avaliação, introdução ao Quartus II e ModelSim

- (Ter. 21/03 - Qui. 23/03): Aula 02: Introdução ao uso do Quartus II

- (Ter. 28/03 - Qui. 30/03): Aula 03: Primeira programação da placa e primeira atividade prática

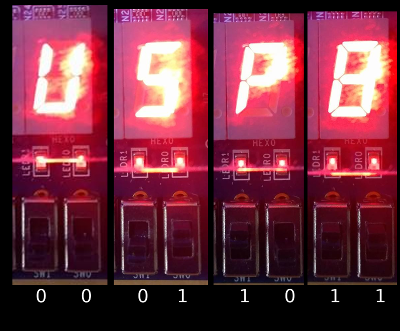

- Primeira atividade prática: Desenvolver um circuito para desenhar as letras U, S e P no primeiro display de sete segmentos do FPGA (HEX0[6..0]) utilizando switches (SW[0] e SW[1]). Lembrar que os segmentos são ativados quando o sinal é 0 e não 1! Saída esperada:

- (Ter. 04/04 - Qui. 06/04): Aula 04: Segunda atividade prática

- Segunda atividade prática (SOMENTE TURMA DE TERÇA): em dupla e apresentar função lógica no papel:

- Temos a seguir uma série de requisitos que um candidato, a uma vaga qualquer, deve preencher. O candidato precisa ser:

- Mulher casada, com 25 anos ou mais, ou;

- Mulher com menos de 25 anos, ou;

- Homem casado com menos de 25 anos que nunca se envolveu com a polícia, ou;

- Homem casado que já tenha se envolvido com a polícia, ou;

- Homem casado, com 25 anos ou mais, que não tenha se envolvido com a polícia.

- As variáveis w, x, y e z assumem o valor verdade 1 nos seguintes casos:

- w = 1 se o candidato tenha se envolvido com a polícia;

- x = 1 se o candidato for casado;

- y = 1 se o candidato for do sexo masculino;

- z = 1 se o candidato tiver menos que 25 anos.

- Implemente um circuito que acenda um led sempre que o candidato estiver apto para a vaga. A entrada do circuito deve ser dada por botões/switches do kit FPGA.

- Segunda atividade prática (SOMENTE TURMA DE QUINTA): em dupla e apresentar função lógica no papel:

- Temos a seguir uma série de requisitos que um candidato, a uma vaga qualquer, deve preencher. O candidato precisa ser:

- Mulher casada, com 25 anos ou mais, ou;

- Mulher com menos de 25 anos, ou;

- Mulher casada que não tenha se envolvido com a polícia, ou;

- Homem casado com menos de 25 anos que nunca se envolveu com a polícia, ou;

- Homem casado, com 25 anos ou mais, que não tenha se envolvido com a polícia.

- As variáveis w, x, y e z assumem o valor verdade 1 nos seguintes casos:

- w = 1 se o candidato tenha se envolvido com a polícia;

- x = 1 se o candidato for casado;

- y = 1 se o candidato for do sexo masculino;

- z = 1 se o candidato tiver menos que 25 anos.

- Implemente um circuito que acenda um led sempre que o candidato estiver apto para a vaga. A entrada do circuito deve ser dada por botões/switches do kit FPGA.

- (Ter. 18/04 - Qui. 20/04): Aula 05: Terceira atividade prática

- Um somador de um bit é dito meio somador (half adder) quando não considera como entrada o bit de transporte (carry);

- Um somador completo (full adder) é quando o mesmo considera este bit de transporte em sua operação de soma~;

- Para desenvolver um somador de n bits, pode-se utilizar 1 meio somador para o bit menos significativo e n-1 somadores completos para os bits restantes. Para a prática de hoje, implemente um hardware somador de 4 bits para números sem sinal (somente magnitude) e exiba os resultados da soma no formato binário e hexadecimal. O que deveria ser feito para exibir o resultado também na base decimal? Utilize o kit FPGA para tal tarefa.

- (Ter. 25/04 - Qui. 27/04): Aula 06: Quarta atividade prática

- Utilizando a mesma formatação numérica e o mesmo hardware do somador completo empregados no exercício da aula anterior (aula 5), implemente agora um multiplicador;

- Observe que na multiplicação, para não haver perda de informação, a quantidade de bits do resultado é a soma da largura do multiplicador com a do multiplicando. Exiba o resultado da multiplicação no formato binário e hexadecimal. Como deveria ser implementado o multiplicador caso os números fossem com sinal?

- (Ter. 02/05 - Qui. 04/05): Aula 07: Quinta atividade prática

- Utilizando o somador de 4 bits e o multiplicador de 4 bits desenvolvido nas práticas anteriores, considerando a representação de complemento de 2 para realizar a subtração, implementar um módulo somador/subtrator/multiplicador com as seguintes entradas e saídas:

- A[3..0]: Primeiro operando, 4 bits, sempre positivo;

- B[3..0]: Segundo operando, 4 bits, sempre positivo;

- S[1..0]: Seletor de operação:

- S[1..0] == 0: Soma (A + B);

- S[1..0] == 1: Subtrair (A - B);

- S[1..0] == 2: Multiplicar (A * B);

- S[1..0] == 3: Indefinido (A ???? B);

- O[7..0]: Resultado da operação selecionada (a saída pode estar em complemento de 2, não precisa converter!);

- Para esta prática, utilizaremos o ModelSim. SELECIONAR A PLACA CYCLONE IV, pois a Cyclone V não tem simulação!

- Utilizando o somador de 4 bits e o multiplicador de 4 bits desenvolvido nas práticas anteriores, considerando a representação de complemento de 2 para realizar a subtração, implementar um módulo somador/subtrator/multiplicador com as seguintes entradas e saídas:

- (Ter. 09/05 - Qui. 11/05): Aula 08: Teste prático

- (Ter. 16/05 - Qui. 18/05): Aula 09: Sexta atividade prática

- Sexta atividade prática (SOMENTE TURMA DE TERÇA):

- Utilizando o circuito implementado na última atividade e mais o uso de MUX/DEMUX, implementar duas novas operaçôes:

- A[3..0]: Primeiro operando, 4 bits, sempre positivo;

- B[3..0]: Segundo operando, 4 bits, sempre positivo;

- S[2..0]: Seletor de operação:

- S[2..0] == 0: Soma (A + B);

- S[2..0] == 1: Subtrair (A - B);

- S[2..0] == 2: Multiplicar (A * B);

- S[2..0] == 3: Shift para esquerda (A << B);

- S[2..0] == 4: Shift para direita (A >> B);

- S[2..0] == 5: Indefinido (A ???? B);

- S[2..0] == 6: Indefinido (A ???? B);

- S[2..0] == 7: Indefinido (A ???? B);

- O[7..0]: Resultado da operação selecionada (a saída pode estar em complemento de 2, não precisa converter!);

- Para esta prática, utilizaremos o ModelSim. SELECIONAR A PLACA CYCLONE IV, pois a Cyclone V não tem simulação!

- Sexta atividade prática (SOMENTE TURMA DE QUINTA):

- Utilizando o circuito implementado na última atividade e mais o uso de MUX/DEMUX, implementar duas novas operaçôes:

- A[3..0]: Primeiro operando, 4 bits, sempre positivo;

- B[3..0]: Segundo operando, 4 bits, sempre positivo;

- S[2..0]: Seletor de operação:

- S[2..0] == 0: Soma (A + B);

- S[2..0] == 1: Subtrair (A - B);

- S[2..0] == 2: Multiplicar (A * B);

- S[2..0] == 3: Rotação para esquerda (A LROT B);

- S[2..0] == 4: Rotação para direita (A RROT B);

- S[2..0] == 5: Indefinido (A ???? B);

- S[2..0] == 6: Indefinido (A ???? B);

- S[2..0] == 7: Indefinido (A ???? B);

- O[7..0]: Resultado da operação selecionada (a saída pode estar em complemento de 2, não precisa converter!);

- Para esta prática, utilizaremos o ModelSim. SELECIONAR A PLACA CYCLONE IV, pois a Cyclone V não tem simulação!

- Exemplos de rotação:

- S[2..0] = 011; A[3..0] = 1011; B[3..0] = 01; O[7..0] = 00000111

- S[2..0] = 011; A[3..0] = 1001; B[3..0] = 11; O[7..0] = 00001100