Mudanças entre as edições de "SSC-117"

(→Informações Gerais) |

(→Links Úteis) |

||

| Linha 52: | Linha 52: | ||

*[http://www.altera.com/education/univ/software/qsim/unv-qsim.html?GSA_pos=1&WT.oss_r=1&WT.oss=Qsim Qsim - Simulador educacional] | *[http://www.altera.com/education/univ/software/qsim/unv-qsim.html?GSA_pos=1&WT.oss_r=1&WT.oss=Qsim Qsim - Simulador educacional] | ||

*[http://www.terasic.com.tw/cgi-bin/page/archive_download.pl?Language=English&No=226&FID=e96456c80e4870fffcb0f2869517fd21 Manual da placa DE2-70] | *[http://www.terasic.com.tw/cgi-bin/page/archive_download.pl?Language=English&No=226&FID=e96456c80e4870fffcb0f2869517fd21 Manual da placa DE2-70] | ||

| + | *[http://www.terasic.com.tw/cgi-bin/page/archive_download.pl?Language=English&No=502&FID=cd9c7c1feaa2467c58c9aa4cc02131af Manual da placa DE2-115] | ||

*[http://dl.dropbox.com/u/39054016/Tutorial%20-%20ModelSim.zip Tutorial de utilização do simulador ModelSim Altera Starter Edition] | *[http://dl.dropbox.com/u/39054016/Tutorial%20-%20ModelSim.zip Tutorial de utilização do simulador ModelSim Altera Starter Edition] | ||

*[https://www.dropbox.com/s/an0uc1jhkzl8co7/990292ad24afe3b5dda0f6144e22c22c.csv?dl=0 Pinos FPGA Cyclone II (DE2-70)] | *[https://www.dropbox.com/s/an0uc1jhkzl8co7/990292ad24afe3b5dda0f6144e22c22c.csv?dl=0 Pinos FPGA Cyclone II (DE2-70)] | ||

Edição das 20h35min de 25 de junho de 2015

Informações Gerais

Disciplina: Introdução à Lógica Digital (SSC-0117) - Somente Laboratório - Semestre: 2015/1

Professor: Dr. Vanderlei Bonato (vbonato at icmc dot usp dot br)

Estagiário PAE: Raphael Fernandes Ribeiro (raphaelf at icmc dot usp dot br)

- Horário de Atendimento

- Professor: A definir.

- Estagiário PAE: Solicite atendimento por e-mail.

- Critérios de Avaliação

- P1 = 40% da Nota Final

- P2 = 60% da Nota Final

- Trabalho Prático 1 = Trabalho + Apresentação = 40% da Nota Final

- Trabalho Prático 2 = Trabalho + Apresentação = 60% da Nota Final

- B = Bônus de 10% para o desenvolvimento de atividades durante as aulas

- A = Arguição individual durante a apresentação de P1 e P2 valendo no máximo 1.

- Nota Final: P1*A + P2*A + B

- Ementa da Disciplina

https://uspdigital.usp.br/jupiterweb/obterDisciplina?sgldis=SSC0117

- DESCRIÇÃO DO PROJETO 1 (P1) PARA ENTREGA NO DIA 14/05/2015

Arquivo:Descricao projeto v1 SSC117.pdf

- DESCRIÇÃO DO PROJETO 2 (P2) PARA ENTREGA NO DIA 02/05/2015

Arquivo:Descricao projeto v2 SSC117.pdf

- Dicas de como construir o multiplicador e o subtrator

http://www.coertvonk.com/family/school/digital-logic-4245

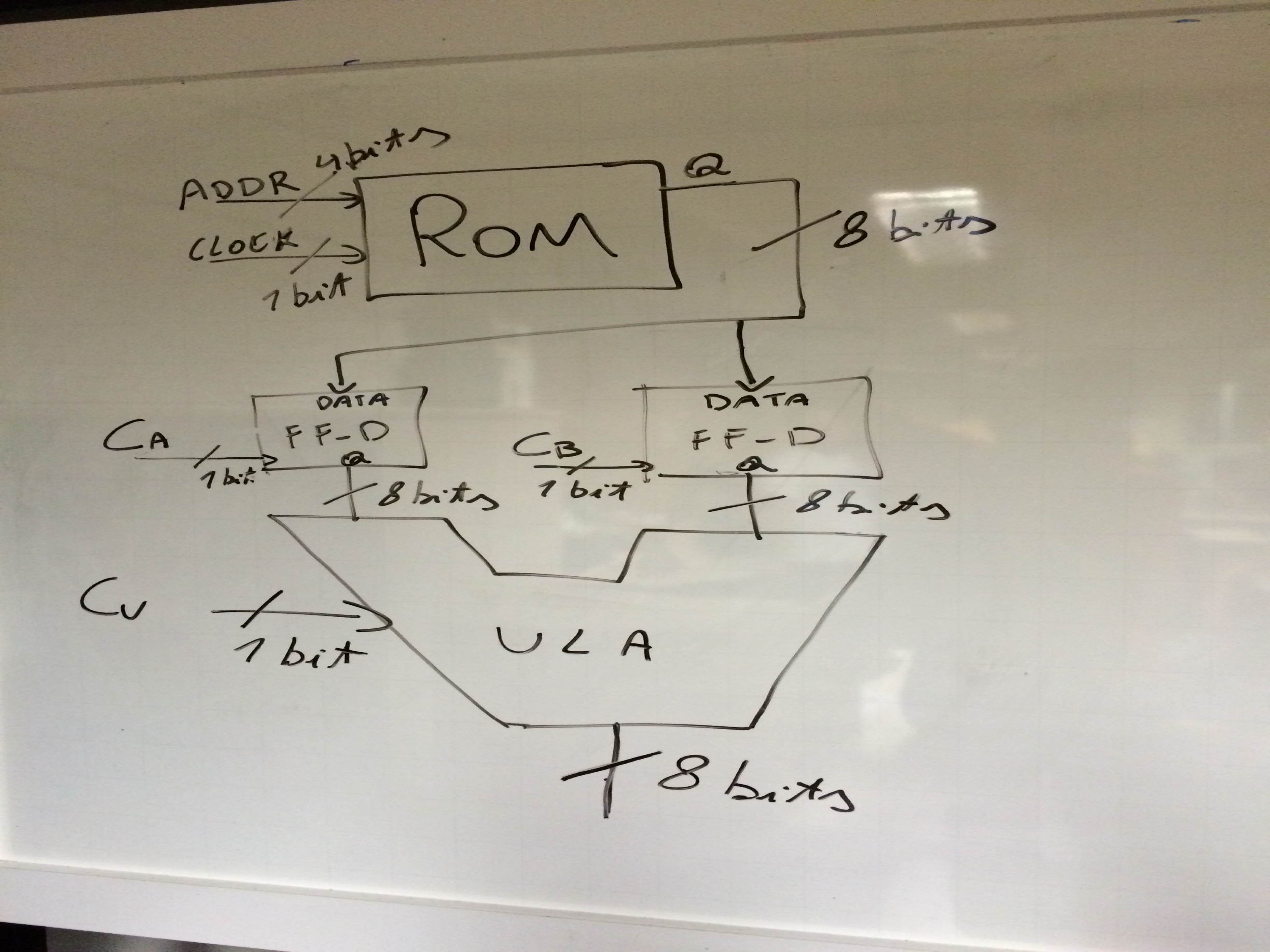

- EXEMPLO DE USO DE MEMORIA ROM

Apostila com aulas Práticas

[1]

Modelo de relatório paras as aulas de laboratório

Arquivo:ModeloRelatório.rar

Tutorial Quartus

Arquivo:GuiaResumido-Quartus II 91.pdf

Links Úteis

- Página de download do Quartus II: https://www.altera.com/download/dnl-index.jsp

- Qsim - Simulador educacional

- Manual da placa DE2-70

- Manual da placa DE2-115

- Tutorial de utilização do simulador ModelSim Altera Starter Edition

- Pinos FPGA Cyclone II (DE2-70)

- Pinos FPGA Cyclone IV (DE2-115)

- Flip-FlopD

- Mem ROM

SSC-117- INTRODUÇÃO A LÓGICA DIGITAL - Semestre: 2014/1

Prof. Alexandre Cláudio Botazzo Delbem

E-mail: acbd@icmc.usp.br

Disponibilidade fora do horário de aula:

Terça-feira, das 14hs as 16hs na sala 4-108

Prof. Onofre Trindade Junior

E-mail: otj@icmc.usp.br

Estagiário PAE: Alexandre Defelicibus

E-mail: adefelicibus@gmail.com

Conforme apresentado em aula, a ementa do curso está no link abaixo:

https://uspdigital.usp.br/jupiterweb/obterDisciplina?sgldis=SSC0117&verdis=1

Avaliação da Disciplina

Teoria

Será avaliado por relatórios práticos e exercícios em aula.

Prática

Será avaliado por relatórios para cada aula de laboratório (deverão ser enviados para o e-mail do professor ao final da aula)

Provinhas extras

Provas adicionais (opcionais) serão aplicadas para avaliar o andamento do conteúdo e para obtenção de uma pontuação extra a nota final.

Média

70% Teoria, média aritmética de duas provas

30% Trabalho na prática

Provas Teóricas

1ª Prova: 07/04/2014

2ª Prova: 02/06/2014

Exercícios

Entregar os exercícios das páginas 36 a 38 do livro

Introdução a Eletrônica Digital na próxima aula (07/04).