SSC-109(bonato) 2018

De CoteiaWiki

Índice

SSC-109 - PRÁTICA EM LÓGICA DIGITAL - 2018/1

Prof. Vanderlei Bonato (PRÁTICA)

E-mail: vbonato@usp.br

Estagiário PAE: André Bannwart Perina

E-mail: abperina@usp.br

Estagiário PAE: Cláudio Roberto Costa

E-mail: claudiocosta@usp.br

FAQ

Para dúvidas frequentes relacionadas à instabilidade emocional do Quartus/ModelSim:

Arquivos

- Descrição da disciplina: Arquivo:ApresentacaoCursoSSC0109 2018.pdf

- Descrição do trabalho final: Arquivo:ProjetoSSC0109 2018.pdf

- Casos de teste para o trabalho final: Arquivo:ProjetoSSC0109 2018 testes.pdf

- Pin mapping DE0-CV: Arquivo:DE0 CV Main Pins.zip

- Pin mapping DE2-115: Arquivo:DE2 115 Main Pins.zip

- Manual DE0-CV: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE0-CV/DE0_CV_User_Manual.pdf

- Manual DE2-115: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE2-115/DE2_115_User_Manual.pdf

Avisos

NOTAS FINAIS NO AR!

TRABALHO FINAL É INDIVIDUAL OU EM DUPLA!

ESPECIFICAÇÃO DO TRABALHO NO AR!

NOTAS DA PROVA PRÁTICA NO AR!

- Datas importantes:

- Prova prática: 10/05

- Trabalho prático principal: 05/07

- Recuperação: 12/07 horário da aula

Notas

- FINAL:

- Quinta 14h: Arquivo:SSC0109 2018 1 4 Final.pdf

- Quinta 16h: Arquivo:SSC0109 2018 1 3 Final.pdf

- Trabalho:

- Quinta 14h: Arquivo:SSC0109 2018 1 4 Trabalho.pdf

- Quinta 16h: Arquivo:SSC0109 2018 1 3 Trabalho.pdf

- Prova Prática:

- Quinta 14h: Arquivo:SSC0109 2018 1 4.pdf

- Quinta 16h: Arquivo:SSC0109 2018 1 3.pdf

Método de avaliação

Para mais detalhes ver arquivo de descrição da disciplina.

- 20% atividades

- 30% prova prática

- 50% trabalho prático principal

Cronograma realizado

- (Qui. 08/03): Aula 01: introdução do curso, apresentação da ementa, critério de avaliação, introdução ao Quartus II e ModelSim

- (Qui. 22/03): Aula 02: introdução ao Quartus II e ModelSim (continuação)

- Executar o circuito da aula anterior na placa de FPGA (pinar manualmente e por nome com o uso de script);

- Utilização do Quartus:

- Uso de script para controle da ferramenta no modo shell;

- Criação de componentes e seu uso em modo hierárquico (definicão do top level);

- Uso de pinos agrupados e de barramentos;

- Conexão de fios e barramentos por meio de nomes;

- Exibição de componentes da biblioteca: aritméticos, lógicos e memórias (incluindo gcc e vcc);

- (Qui. 05/04): Aula 03: primeira atividade prática

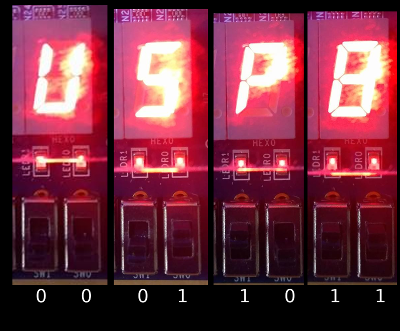

- Desenvolver um circuito para desenhar as letras U, S e P no primeiro display de sete segmentos do FPGA (HEX0[6..0]) utilizando switches (SW[0] e SW[1]). Lembrar que os segmentos são ativados quando o sinal é 0 e não 1! Saída esperada:

- (Qui. 12/04): Aula 04: segunda atividade prática

- Desenvolver um módulo para, dado quatro bits de entrada, exibir estes bits no display de sete segmentos no formato hexadecimal (0, 1, 2, ..., D, E, F). Exemplos:

- SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 0, HEX0[6..0] = 0

- SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 1, HEX0[6..0] = 1

- ...

- SW[3] = 0, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = 7

- ...

- SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 0, HEX0[6..0] = E

- SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = F

- Desenvolver um módulo para, dado quatro bits de entrada, exibir estes bits no display de sete segmentos no formato hexadecimal (0, 1, 2, ..., D, E, F). Exemplos:

- (Qui. 19/04): Aula 05: terceira atividade prática

- Um somador de um bit é dito meio somador (half adder) qndo nao considera como entrada o bit de transporte (carry) e somador completo (full adder) qndo o mesmo considera este bit de transporte em sua operação de soma. Para desenvolver um somador de n bits, pode-se utilizar 1 meio somador para o bit menos significativo e n-1 somadores completos para os bits restantes. Para a prática de hoje, implemente um hardware somador de 8 bits para números sem sinal (somente magnitude) e exiba os resultados da soma no formato binário e hexadecimal. O que deveria ser feito para exibir o resultado também na base decimal? Utilize o kit FPGA para tal tarefa.

- (Qui. 26/04): Aula 06: quarta atividade prática

- Utilizando a mesma formatação numérica e o mesmo hardware do somador completo empregados no exercício da aula anterior (aula 5), implemente agora um multiplicador. Observe que na multiplicação, para não haver perda de informação, a quantidade de bits do resultado é a soma da largura do Multiplicador com a do Multiplicando. Exiba o resultado da multiplicação no formato binário e hexadecimal. Como deveria ser implementado o multiplicador caso os números fossem com sinal?

- (Qui. 03/05): Aula 07: quinta atividade prática

- O hardware subtrator pode ser facilmente obtido a partir do circuito somador da terceira atividade prática, desde que seja adotado o padrão de números em complemento de 2 para a representação do subtraendo. Com o uso do complemento de 2 no subtraendo a subtração é obtida por meio da soma do minuendo com o subtraendo. Para esta atividade prática, estenda o hardware do somador para que o mesmo suporte as duas operações soma e subtração, assumindo para isso o uso de números em complemento de 2. Exiba os resultados da operação em hexadecimal indicando inclusive o sinal do número. IMPLEMENTAR UTILIZANDO O MODELSIM

- (Qui. 10/05): Aula 08: P1

- (Qui. 17/05): Aula 09: sexta atividade prática

- Crie um circuito para deslocar (shift) uma palavra de 4 bits (nibble) n posições para a esquerda. O deslocamento (n) pode variar de zero até a quantidade de bits da palavra (no caso, 4). Utilize MUX/DEMUX para resolver o problema.

- (Qui. 24/05): Aula 10: sétima atividade prática

- Implementar encoder e decoder binários.

- O encoder é um circuito onde N bits geram log(N) bits de saída. Apenas um bit da entrada pode estar ativo por vez. A posição do bit ativo define o número binário na saída, como mostra a tabela verdade para um encoder 4-para-2 (pode ser generalizado para qualquer número de bits):

- Implementar encoder e decoder binários.

| Entradas || Saídas| | I3 I2 I1 I0 || O1 O0 | | 0 0 0 1 || 0 0 | | 0 0 1 0 || 0 1 | | 0 1 0 0 || 1 0 | | 1 0 0 0 || 1 1 | | Outros casos|| X X |

- O decoder é justamente o caso contrário: log(N) bits de entrada definem N bits de saída, onde apenas 1 bit de saída é ativo por vez:

| Entr. || Saídas | | I1 I0 || O3 O2 O1 O0 | | 0 0 || 0 0 0 1 | | 0 1 || 0 0 1 0 | | 1 0 || 0 1 0 0 | | 1 1 || 1 0 0 0 |

- (Qui. 07/06): Aula 11: oitava atividade prática

- Considerando as práticas das aulas 6 e 7, desenvolva um circuito multiplicador que suporte a operação com números em complemento de 2. Adote a largura de 4 bits para os operandos e o resultado deverá conter a quantidade de bits necessária para que nunca ocorra estouro (overflow) no resultado. O circuito pode ser demonstrado no ModelSim ou na placa de FPGA. O trabalho pode ser desenvolvido em dupla.

- (Qui. 14/06): Aula 12: explicação do divisor combinacional e início da implementação do trabalho final

- (Qui. 21/06): Aula 13: implementação trabalho final

- (Qui. 28/06): Aula 14: implementação trabalho final

- (Qui. 05/07): Aula 15: entrega trabalho final