Mudanças entre as edições de "SSC-109(bonato) 2018"

De CoteiaWiki

| Linha 62: | Linha 62: | ||

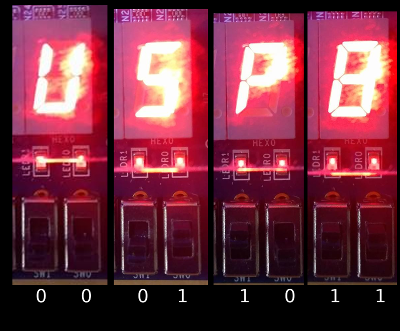

*** SW[0] = 1 e SW[1] = 1: Tudo apagado ou tudo aceso | *** SW[0] = 1 e SW[1] = 1: Tudo apagado ou tudo aceso | ||

*** [[Arquivo:ssc109at1.png]] | *** [[Arquivo:ssc109at1.png]] | ||

| + | * '''(Qui. 12/04): Aula 04: segunda atividade prática''' | ||

| + | ** Desenvolver um módulo para, dado quatro bits de entrada, exibir estes bits no display de sete segmentos no formato hexadecimal (0, 1, 2, ..., D, E, F). Exemplos: | ||

| + | *** SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 0, HEX0[6..0] = 0 | ||

| + | *** SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 1, HEX0[6..0] = 1 | ||

| + | *** ... | ||

| + | *** SW[3] = 0, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = 7 | ||

| + | *** ... | ||

| + | *** SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 0, HEX0[6..0] = E | ||

| + | *** SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = F | ||

Edição das 19h54min de 12 de abril de 2018

Índice

SSC-109 - PRÁTICA EM LÓGICA DIGITAL - 2018/1

Prof. Vanderlei Bonato (PRÁTICA)

E-mail: vbonato@usp.br

Estagiário PAE: André Bannwart Perina

E-mail: abperina@usp.br

Estagiário PAE: Cláudio Roberto Costa

E-mail: claudiocosta@usp.br

FAQ

Para dúvidas frequentes relacionadas à instabilidade emocional do Quartus/ModelSim:

Arquivos

- Descrição da disciplina: Arquivo:ApresentacaoCursoSSC0109 2018.pdf

- Pin mapping DE0-CV: Arquivo:DE0 CV Main Pins.zip

- Pin mapping DE2-115: Arquivo:DE2 115 Main Pins.zip

- Manual DE0-CV: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE0-CV/DE0_CV_User_Manual.pdf

- Manual DE2-115: ftp://ftp.altera.com/up/pub/Altera_Material/Boards/DE2-115/DE2_115_User_Manual.pdf

Avisos

- Datas importantes:

- Prova prática: 10/05

- Trabalho prático principal: 28/06

- Recuperação:

Notas

Método de avaliação

Para mais detalhes ver arquivo de descrição da disciplina.

- 20% atividades

- 30% prova prática

- 50% trabalho prático principal

Cronograma realizado

- (Qui. 08/03): Aula 01: introdução do curso, apresentação da ementa, critério de avaliação, introdução ao Quartus II e ModelSim

- (Qui. 22/03): Aula 02: introdução ao Quartus II e ModelSim (continuação)

- Executar o circuito da aula anterior na placa de FPGA (pinar manualmente e por nome com o uso de script);

- Utilização do Quartus:

- Uso de script para controle da ferramenta no modo shell;

- Criação de componentes e seu uso em modo hierárquico (definicão do top level);

- Uso de pinos agrupados e de barramentos;

- Conexão de fios e barramentos por meio de nomes;

- Exibição de componentes da biblioteca: aritméticos, lógicos e memórias (incluindo gcc e vcc);

- (Qui. 05/04): Aula 03: primeira atividade prática

- Desenvolver um circuito para desenhar as letras U, S e P no primeiro display de sete segmentos do FPGA (HEX0[6..0]) utilizando switches (SW[0] e SW[1]). Lembrar que os segmentos são ativados quando o sinal é 0 e não 1! Saída esperada:

- (Qui. 12/04): Aula 04: segunda atividade prática

- Desenvolver um módulo para, dado quatro bits de entrada, exibir estes bits no display de sete segmentos no formato hexadecimal (0, 1, 2, ..., D, E, F). Exemplos:

- SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 0, HEX0[6..0] = 0

- SW[3] = 0, SW[2] = 0, SW[1] = 0, SW[0] = 1, HEX0[6..0] = 1

- ...

- SW[3] = 0, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = 7

- ...

- SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 0, HEX0[6..0] = E

- SW[3] = 1, SW[2] = 1, SW[1] = 1, SW[0] = 1, HEX0[6..0] = F

- Desenvolver um módulo para, dado quatro bits de entrada, exibir estes bits no display de sete segmentos no formato hexadecimal (0, 1, 2, ..., D, E, F). Exemplos: